# FM3130 Integrated RTC/Alarm and 64Kb F-RAM

# Features

#### **High Integration Device Replaces Multiple Parts**

- Serial Nonvolatile Memory

- Real-time Clock (RTC) with Alarm

- Clock Output (Programmable frequency)

#### 64Kb Ferroelectric Nonvolatile RAM

- Internally Organized as 8Kx8

- Unlimited Read/Write Endurance

- 10 year Data Retention

- NoDelay<sup>TM</sup> Writes

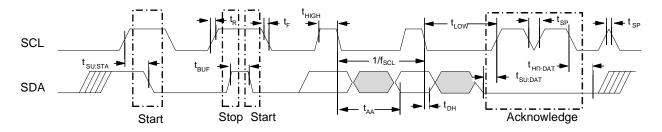

#### **Fast Two-wire Serial Interface**

- Up to 1 MHz Maximum Bus Frequency

- Supports Legacy Timing for 100 kHz & 400 kHz

- RTC & F-RAM Controlled via 2-wire Interface

# Description

The FM3130 integrates a real-time clock (RTC) and F-RAM nonvolatile memory. The device operates from 2.7 to 3.6V.

The FM3130 provides nonvolatile F-RAM which features fast write speed and unlimited endurance. This allows the memory to serve as extra RAM for the system microcontroller or conventional nonvolatile storage. This memory is truly nonvolatile rather than battery backed.

The real-time clock (RTC) provides time and date information in BCD format. It can be permanently powered from external backup voltage source, either a battery or a capacitor. The timekeeper uses a common external 32.768 kHz crystal and provides a calibration mode that allows software adjustment of timekeeping accuracy.

# Real-time Clock/Calendar

- Backup Current under 1 µA

- Seconds through Centuries in BCD format

- Tracks Leap Years through 2099

- Uses Standard 32.768 kHz Crystal (12.5pF)

- Software Calibration

•

• Supports Battery or Capacitor Backup

#### **Easy to Use Configurations**

- Operates from 2.7 to 3.6V

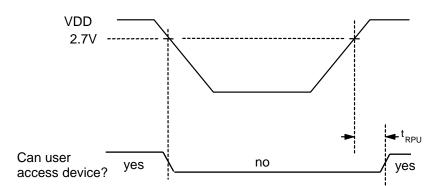

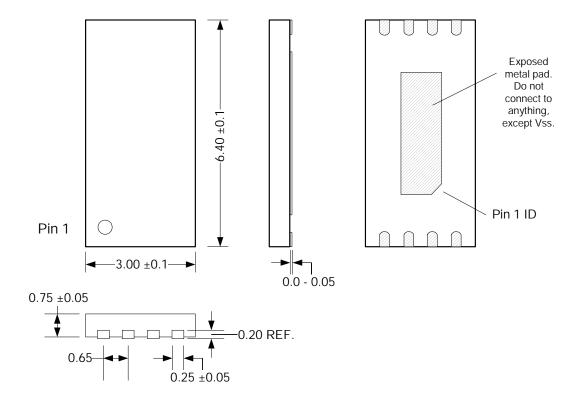

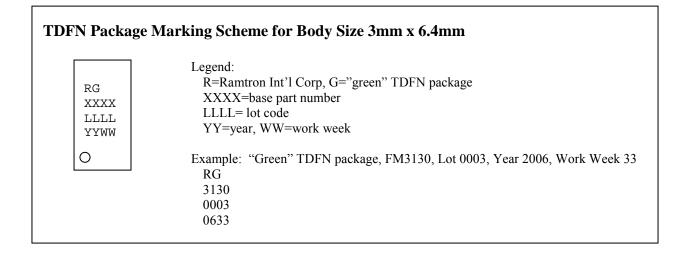

- 8-pin "Green" SOIC (-G) and TDFN (-DG)

- Low Operating Current

- Industrial Temperature -40°C to +85°C

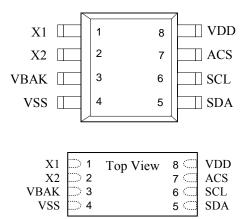

# **Pin Configuration**

| Pin Name | Function                 |

|----------|--------------------------|

| X1, X2   | Crystal Connections      |

| ACS      | Alarm/Calibration/SqWave |

| SDA      | Serial Data              |

| SCL      | Serial Clock             |

| VBAK     | Battery-Backup Supply    |

| VDD      | Supply Voltage           |

| VSS      | Ground                   |

| Ordering Information |                         |  |  |  |  |  |

|----------------------|-------------------------|--|--|--|--|--|

| FM3130-G             | "Green"/RoHS 8-pin SOIC |  |  |  |  |  |

| FM3130-DG            | "Green"/RoHS 8-pin TDFN |  |  |  |  |  |

This product conforms to specifications per the terms of the Ramtron standard warranty. The product has completed Ramtron's internal qualification testing and has reached production status.

Ramtron International Corporation 1850 Ramtron Drive, Colorado Springs, CO 80921 (800) 545-FRAM, (719) 481-7000 http://www.ramtron.com

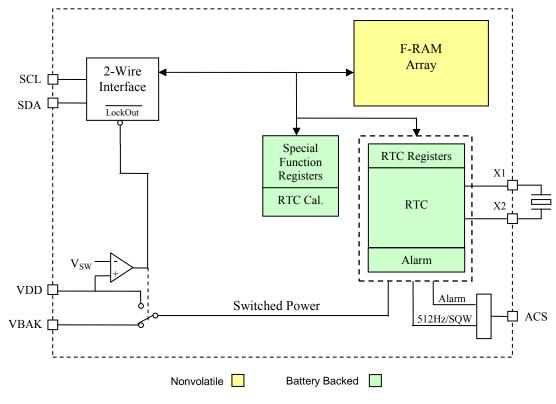

Figure 1. Block Diagram

# **Pin Descriptions**

| Pin Name | Туре   | Pin Description                                                                            |

|----------|--------|--------------------------------------------------------------------------------------------|

| X1, X2   | I/O    | 32.768 kHz crystal connection. When using an external oscillator, apply the clock to X1    |

|          |        | and a DC mid-level to X2 (see Crystal Type section for suggestions).                       |

| ACS      | Output | Alarm/Calibration/SquareWave: This is an open-drain output that requires an external       |

|          |        | pullup resistor. The alarm, calibration, and square wave functions all share this output.  |

|          |        | In Alarm mode, this pin acts as the active-low alarm output. In Calibration mode, a 512    |

|          |        | Hz square-wave is driven out. In SquareWave mode, the user may select a frequency of       |

|          |        | 1, 512, 4096, or 32768 Hz to be used as a continuous output. Refer to Table 3. Control     |

|          |        | Bit Settings for ACS Pin to determine the bit settings for each mode.                      |

| SDA      | I/O    | Serial Data & Address: This is a bi-directional line for the two-wire interface. It is     |

|          |        | open-drain and is intended to be wire-OR'd with other devices on the two-wire bus. The     |

|          |        | input buffer incorporates a Schmitt trigger for noise immunity and the output driver       |

|          |        | includes slope control for falling edges. A pull-up resistor is required.                  |

| SCL      | Input  | Serial Clock: The serial clock line for the two-wire interface. Data is clocked out of the |

|          | _      | part on the falling edge, and data into the device on the rising edge. The SCL input also  |

|          |        | incorporates a Schmitt trigger input for noise immunity.                                   |

| VBAK     | Supply | Backup supply voltage: A 3V battery or a large value capacitor. If no backup supply is     |

|          |        | used, this pin should be tied to $V_{SS}$ .                                                |

| VDD      | Supply | Supply Voltage.                                                                            |

| VSS      | Supply | Ground                                                                                     |

# Overview

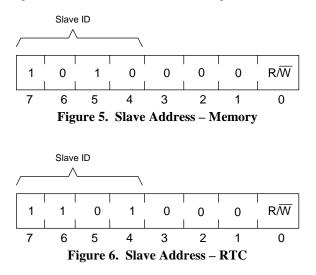

The FM3130 device combines a serial nonvolatile RAM with a real-time clock (RTC) and alarm. These complementary but distinct functions share a common interface in a single package. Although monolithic, the product is organized as two logical devices, the F-RAM memory and the RTC/alarm. From the system perspective, they appear to be two separate devices with unique IDs on the serial bus.

The memory is organized as a stand-alone 2-wire nonvolatile memory with a standard device ID value. The real-time clock and alarm are accessed with a separate 2-wire device ID. This allows clock/calendar data to be read while maintaining the most recently used memory address. The clock and alarm are controlled by 15 special function registers. The registers are maintained by the power source on the VBAK pin, allowing them to operate from battery or backup capacitor power when  $V_{DD}$  drops below a set threshold. Each functional block is described below.

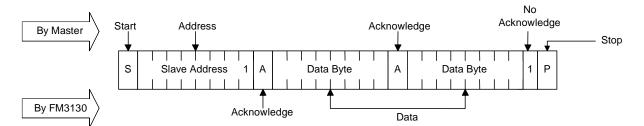

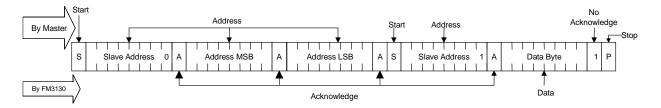

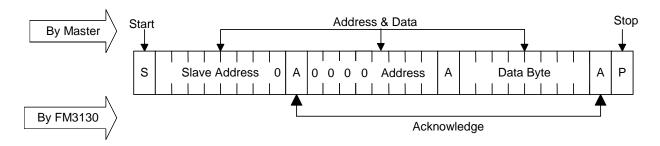

# **Memory Operation**

The FM3130 integrates a 64Kb F-RAM. The memory is organized in bytes, 8192 addresses of 8 bits each. The memory is based on F-RAM technology. Therefore it can be treated as RAM and is read or written at the speed of the two-wire bus with no delays for write operations. It also offers effectively unlimited write endurance unlike other nonvolatile memory technologies. The two-wire interface protocol is described further on page 12.

The memory array can be write-protected by software. Two bits (WP0, WP1) in register 0Eh control the protection setting as shown in the following table. Based on the setting, the protected addresses cannot be written and the 2-wire interface will not acknowledge any data to protected addresses. The special function registers containing these bits are described in detail below.

Table 1. F-RAM Write-Protect

| Write-Protect Range | WP1 | WP0 |

|---------------------|-----|-----|

| None                | 0   | 0   |

| Bottom 1/4          | 0   | 1   |

| Bottom 1/2          | 1   | 0   |

| Full array          | 1   | 1   |

The WP bits are battery-backed. On a powerup without a backup source, the WP bits are cleared to a '0' state.

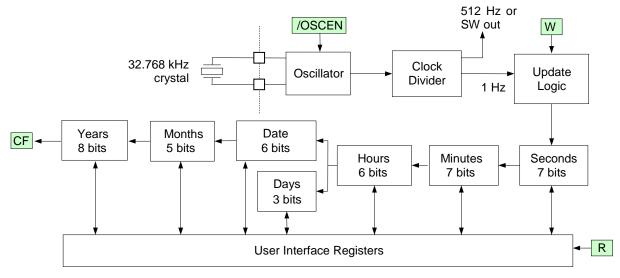

# **Real-Time Clock Operation**

The real-time clock (RTC) is a timekeeping device that can be battery or capacitor backed for permanently-powered operation. It offers a software calibration feature that allows high accuracy.

The RTC consists of an oscillator, clock divider, and a register system for user access. It divides down the 32.768 kHz time-base and provides a minimum resolution of seconds (1Hz). Static registers provide the user with read/write access to the time values. It includes registers for seconds, minutes, hours, dayof-the-week, date, months, and years. A block diagram (Figure 2) illustrates the RTC function.

The user registers are synchronized with the timekeeper core using R and W bits in register 00h described below. Changing the R bit from 0 to 1 transfers timekeeping information from the core into holding registers that can be read by the user. If a timekeeper update is pending when R is set, then the core will be updated prior to loading the user registers. The registers are frozen and will not be updated again until the R bit is cleared to '0'. R is used to read the time.

Setting the W bit to '1' locks the user registers. Clearing it to a '0' causes the values in the user registers to be loaded into the timekeeper core. W is used for writing new time values. Users should be certain not to load invalid values, such as FFh, to the timekeeping registers. Updates to the timekeeping core occur continuously except when locked. All timekeeping registers must be initialized at the first powerup or when the LB bit is set. See the description of the LB bit on page 11.

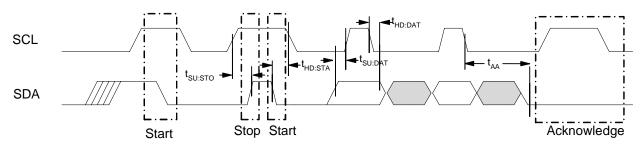

# **Backup Power**

The real-time clock/calendar is intended to be permanently powered. When the primary system power fails, the voltage on the  $V_{DD}$  pin will drop. When  $V_{DD}$  is less than  $V_{SW}$ , the RTC will switch to the backup power supply on  $V_{BAK}$ . The clock operates at extremely low current in order to maximize battery or capacitor life. However, an advantage of combining a clock function with F-RAM memory is that data is not lost regardless of the backup power source.

If a battery is applied without a  $V_{DD}$  power supply, the device has been designed to ensure the  $I_{BAK}$ current does not exceed the 1µA maximum limit.

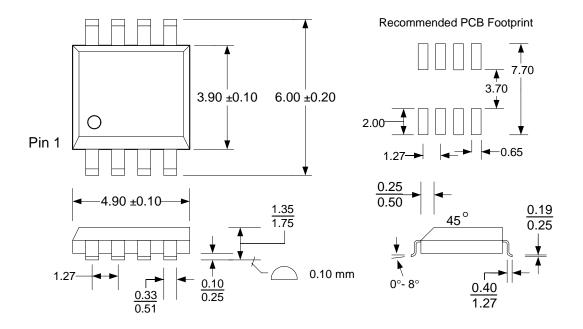

#### **Trickle Charger**

To facilitate capacitor backup the  $V_{BAK}$  pin can optionally provide a trickle charge current. When the

- In the case where no battery is used, the  $V_{\text{BAK}}$  pin should be tied to  $V_{\text{SS}}.$

<sup>b</sup> Note: systems using lithium batteries should clear the VBC bit to 0 to prevent battery charging. The  $V_{BAK}$  circuitry includes an internal 1 K $\Omega$  series resistor as a safety element.

Figure 2. Real-Time Clock Core Block Diagram

# Calibration

When the CAL bit in register 00h is set to '1', the clock enters calibration mode. In calibration mode, the ACS output pin is dedicated to the calibration function and the power fail output is temporarily unavailable. Calibration operates by applying a digital correction to the counter based on the frequency error. In this mode, the ACS pin is driven with a 512 Hz (nominal) square wave. Any measured deviation from 512 Hz translates into a timekeeping error. The user converts the measured error in ppm and writes the appropriate correction value to the calibration register. The correction factors are listed in the table below. Positive ppm errors require a negative adjustment that removes pulses. Negative ppm errors require a positive correction that adds pulses. Positive ppm adjustments have the CALS (sign) bit set to '1', whereas negative ppm adjustments have CALS = 0. After calibration, the clock will have a maximum error of  $\pm 2.17$  ppm or  $\pm$  0.09 minutes per month at the calibrated temperature.

The calibration setting is battery-backed and must be reloaded should the backup source fail. It is accessed with bits CAL.4-0 in register 01h. This value only can be written when the CAL bit is set to a '1'. To exit the calibration mode, the user must clear the CAL bit to a '0'. When the CAL bit is '0', the ACS pin will revert to another function as defined in *Table 3. Control Bit Settings for ACS Pin.*

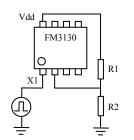

# **Crystal Type**

The crystal oscillator is designed to use a 12.5pF crystal without the need for external components, such as loading capacitors. The FM3130 device has built-in loading capacitors that match the crystal.

If a 32.768kHz crystal is not used, an external oscillator may be connected to the FM3130. Apply the oscillator to the X1 pin. Its high and low voltage levels can be driven rail-to-rail or amplitudes as low as approximately 500mV p-p. To ensure proper operation, a DC bias must be applied to the X2 pin. It should be centered between the high and low levels on the X1 pin. This can be accomplished with a voltage divider. See Figure 3.

Figure 3. External Oscillator

In the example, R1 and R2 are chosen such that the X2 voltage is centered around the oscillator drive levels. If you wish to avoid the DC current, you may

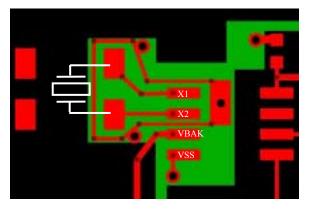

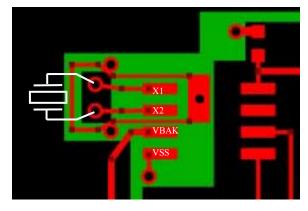

**Layout for Surface Mount Crystal** (red = top layer, green = bottom layer)

choose to drive X1 with an external clock and X2 with an inverted clock using a CMOS inverter.

#### Layout Recommendations

The X1 and X2 crystal pins employ very high impedance circuits and the oscillator connected to these pins can be upset by noise or extra loading. To reduce RTC clock errors from signal switching noise, a guard ring should be placed around these pads and the guard ring grounded. SDA and SCL traces should be routed away from the X1/X2 pads. The X1 and X2 trace lengths should be less than 5 mm. The use of a ground plane on the backside or inner board layer is preferred. See layout example. Red is the top layer, green is the bottom layer.

**Layout for Through Hole Crystal** (red = top layer, green = bottom layer)

|    | Positive     | Calibration for slow | clocks: Calibra | tion will achieve | $\pm$ 2.17 PPM after calibration |

|----|--------------|----------------------|-----------------|-------------------|----------------------------------|

|    | Measured Fre | equency Range        | Error Range (   | PPM)              |                                  |

|    | Min          | Max                  | Min             | Max               | Program Calibration Register to: |

| 0  | 512.0000     | 511.9989             | 0               | 2.17              | 000000                           |

| 1  | 511.9989     | 511.9967             | 2.18            | 6.51              | 100001                           |

| 2  | 511.9967     | 511.9944             | 6.52            | 10.85             | 100010                           |

| 3  | 511.9944     | 511.9922             | 10.86           | 15.19             | 100011                           |

| 4  | 511.9922     | 511.9900             | 15.20           | 19.53             | 100100                           |

| 5  | 511.9900     | 511.9878             | 19.54           | 23.87             | 100101                           |

| 6  | 511.9878     | 511.9856             | 23.88           | 28.21             | 100110                           |

| 7  | 511.9856     | 511.9833             | 28.22           | 32.55             | 100111                           |

| 8  | 511.9833     | 511.9811             | 32.56           | 36.89             | 101000                           |

| 9  | 511.9811     | 511.9789             | 36.90           | 41.23             | 101001                           |

| 10 | 511.9789     | 511.9767             | 41.24           | 45.57             | 101010                           |

| 11 | 511.9767     | 511.9744             | 45.58           | 49.91             | 101011                           |

| 12 | 511.9744     | 511.9722             | 49.92           | 54.25             | 101100                           |

| 13 | 511.9722     | 511.9700             | 54.26           | 58.59             | 101101                           |

| 14 | 511.9700     | 511.9678             | 58.60           | 62.93             | 101110                           |

| 15 | 511.9678     | 511.9656             | 62.94           | 67.27             | 101111                           |

| 16 | 511.9656     | 511.9633             | 67.28           | 71.61             | 110000                           |

| 17 | 511.9633     | 511.9611             | 71.62           | 75.95             | 110001                           |

| 18 | 511.9611     | 511.9589             | 75.96           | 80.29             | 110010                           |

| 19 | 511.9589     | 511.9567             | 80.30           | 84.63             | 110011                           |

| 20 | 511.9567     | 511.9544             | 84.64           | 88.97             | 110100                           |

| 21 | 511.9544     | 511.9522             | 88.98           | 93.31             | 110101                           |

| 22 | 511.9522     | 511.9500             | 93.32           | 97.65             | 110110                           |

| 23 | 511.9500     | 511.9478             | 97.66           | 101.99            | 110111                           |

#### **Table 2. Calibration Adjustments**

#### FM3130 Integrated RTC/Alarm with 64Kb FRAM

| 24 | 511.9478 | 511.9456 | 102.00 | 106.33 | 111000 |

|----|----------|----------|--------|--------|--------|

| 25 | 511.9456 | 511.9433 | 106.34 | 110.67 | 111001 |

| 26 | 511.9433 | 511.9411 | 110.68 | 115.01 | 111010 |

| 27 | 511.9411 | 511.9389 | 115.02 | 119.35 | 111011 |

| 28 | 511.9389 | 511.9367 | 119.36 | 123.69 | 111100 |

| 29 | 511.9367 | 511.9344 | 123.70 | 128.03 | 111101 |

| 30 | 511.9344 | 511.9322 | 128.04 | 132.37 | 111110 |

| 31 | 511.9322 | 511.9300 | 132.38 | 136.71 | 111111 |

|    | Negative     | Calibration for fast | clocks: Calibrat | tion will achieve | $\pm$ 2.17 PPM after calibration |

|----|--------------|----------------------|------------------|-------------------|----------------------------------|

|    | Measured Fre | equency Range        | Error Ran        | ge (PPM)          |                                  |

|    | Min          | Max                  | Min              | Max               | Program Calibration Register to: |

| 0  | 512.0000     | 512.0011             | 0                | 2.17              | 000000                           |

| 1  | 512.0011     | 512.0033             | 2.18             | 6.51              | 000001                           |

| 2  | 512.0033     | 512.0056             | 6.52             | 10.85             | 000010                           |

| 3  | 512.0056     | 512.0078             | 10.86            | 15.19             | 000011                           |

| 4  | 512.0078     | 512.0100             | 15.20            | 19.53             | 000100                           |

| 5  | 512.0100     | 512.0122             | 19.54            | 23.87             | 000101                           |

| 6  | 512.0122     | 512.0144             | 23.88            | 28.21             | 000110                           |

| 7  | 512.0144     | 512.0167             | 28.22            | 32.55             | 000111                           |

| 8  | 512.0167     | 512.0189             | 32.56            | 36.89             | 001000                           |

| 9  | 512.0189     | 512.0211             | 36.90            | 41.23             | 001001                           |

| 10 | 512.0211     | 512.0233             | 41.24            | 45.57             | 001010                           |

| 11 | 512.0233     | 512.0256             | 45.58            | 49.91             | 001011                           |

| 12 | 512.0256     | 512.0278             | 49.92            | 54.25             | 001100                           |

| 13 | 512.0278     | 512.0300             | 54.26            | 58.59             | 001101                           |

| 14 | 512.0300     | 512.0322             | 58.60            | 62.93             | 001110                           |

| 15 | 512.0322     | 512.0344             | 62.94            | 67.27             | 001111                           |

| 16 | 512.0344     | 512.0367             | 67.28            | 71.61             | 010000                           |

| 17 | 512.0367     | 512.0389             | 71.62            | 75.95             | 010001                           |

| 18 | 512.0389     | 512.0411             | 75.96            | 80.29             | 010010                           |

| 19 | 512.0411     | 512.0433             | 80.30            | 84.63             | 010011                           |

| 20 | 512.0433     | 512.0456             | 84.64            | 88.97             | 010100                           |

| 21 | 512.0456     | 512.0478             | 88.98            | 93.31             | 010101                           |

| 22 | 512.0478     | 512.0500             | 93.32            | 97.65             | 010110                           |

| 23 | 512.0500     | 512.0522             | 97.66            | 101.99            | 010111                           |

| 24 | 512.0522     | 512.0544             | 102.00           | 106.33            | 011000                           |

| 25 | 512.0544     | 512.0567             | 106.34           | 110.67            | 011001                           |

| 26 | 512.0567     | 512.0589             | 110.68           | 115.01            | 011010                           |

| 27 | 512.0589     | 512.0611             | 115.02           | 119.35            | 011011                           |

| 28 | 512.0611     | 512.0633             | 119.36           | 123.69            | 011100                           |

| 29 | 512.0633     | 512.0656             | 123.70           | 128.03            | 011101                           |

| 30 | 512.0656     | 512.0678             | 128.04           | 132.37            | 011110                           |

| 31 | 512.0678     | 512.0700             | 132.38           | 136.71            | 011111                           |

#### Alarm

The alarm function compares user-programmed alarm values to the corresponding RTC time/date values. When a match occurs, an alarm event occurs. The alarm event sets an internal flag AF (register 00h, bit 6) and drives the ACS pin low, if the appropriate control bits are set in registers 00h and 0Eh. See Table 3. The alarm condition on the ACS pin and the AF bit are cleared by reading register 00h.

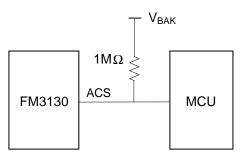

The alarm operates under  $V_{DD}$  or  $V_{BAK}$  power. If the system controller is being used to detect an alarm while the FM3130 is powered on  $V_{BAK}$  only, the ACS pin may cause extra  $I_{BAK}$  current when the alarm is activated. To avoid battery drain, the ACS pin can be

tri-stated by reading the AF flag, located in the RTC/Alarm Control register 00h.

There are five alarm match fields. They are Month, Date, Hours, Minutes, and Seconds. Each of these fields also has a Match bit that is used to determine if the field is used in the alarm match logic. Setting the Match bit to '0' indicates that the corresponding field will be used in the match process.

Depending on the Match bits, the alarm can occur as specifically as one particular second on one day of the month, or as frequently as once per second continuously. The MSB of each Alarm register is a Match bit. Examples of the Match bit settings are shown in *Table 4. Alarm Match Bit Examples*. Selecting none of the match bits (all '1's) indicates that no match is required. The alarm occurs every

second. Setting the match select bit for seconds to '0' causes the logic to match the seconds alarm value to the current time of day. Since a match will occur for only one value per minute, the alarm occurs once per minute. Likewise setting the seconds and minutes match select bits causes an exact match of these values. Thus, an alarm will occur once per hour. Setting seconds, minutes, and hours causes a match once per day. See Table 4 for other alarm setting examples.

# Function of the ACS Pin

The ACS pin is a multifunction pin. The alarm, calibration, and square wave functions all share this output. There are two ways a user can detect an alarm event, by reading the AF flag or by monitoring the ACS pin. An interrupt pin on the host processor may be used to detect an alarm event. The AF flag in the register 00h (bit 6) will indicate that a time/date match has occurred. When a match occurs, the AF bit will be set to '1' and the ACS pin will drive low. The flag and ACS pin will remain in this state until the RTC/Alarm Control register is read which clears the AF bit.

Table 3 that shows the relationship between register control settings and the function of the ACS pin.

Table 3. Control Bit Settings for ACS Pin

| State | e of Reg | Function of<br>ACS pin |             |  |

|-------|----------|------------------------|-------------|--|

| CAL   | AEN      |                        |             |  |

| 0     | 1        | 1                      | /Alarm      |  |

| 0     | Х        | 0                      | Sq Wave out |  |

| 1     | Х        | Х                      | 512 Hz out  |  |

| 0     | 0        | 1                      | Hi-Z        |  |

Table 4. Alarm Match Bit Examples

# Cal Output/SquareWave Output

When the RTC calibration mode is invoked by setting the CAL bit (register 00h, bit 2), the ACS output pin will be driven with a 512 Hz square wave and the alarm will continue to operate. Since most users only invoke the calibration mode during production, this should have no impact on the otherwise normal operation of the alarm.

The ACS output may also be used to drive the system with a continuous frequency. The AL/SW bit (register 0Eh, bit 7) must be a '0'. A user-selectable frequency is provided by F0 and F1 (register 0Eh, bits 5 and 6). The frequencies are 1, 512, 4096, and 32768 Hz. If a continuous frequency output is enabled by using the 512Hz or SquareWave out functions, the alarm function will not be available.

Figure 4. ACS Pin Requires Pullup

The ACS pin is an open-drain output that needs to be pulled up to a supply. The ACS pin and pullup resistor draws current only when the alarm is triggered.

| Seconds | Minutes | Hours | Date | Months | Alarm condition                                                |  |  |  |

|---------|---------|-------|------|--------|----------------------------------------------------------------|--|--|--|

| 1       | 1       | 1     | 1    | 1      | 1 No match required = alarm 1/second                           |  |  |  |

| 0       | 1       | 1     | 1    | 1      | Alarm when seconds match = alarm 1/minute                      |  |  |  |

| 0       | 0       | 1     | 1    | 1      | Alarm when seconds, minutes match = alarm 1/hour               |  |  |  |

| 0       | 0       | 0     | 1    | 1      | Alarm when seconds, minutes, hours match = alarm 1/date        |  |  |  |

| 0       | 0       | 0     | 0    | 1      | Alarm when seconds, minutes, hours, date match = alarm 1/month |  |  |  |

# **Register Map**

The RTC, alarm, and other functions are accessed via 15 special function registers mapped to a separate 2-wire device ID. The interface protocol is described below. The registers contain timekeeping data, control bits, or information flags. A description of each register follows the summary table below.

# **Register Map Summary Table**

| Address | D7     | D6   | D5          | D4      | D3   | D2    | D1      | D0   | Function           | Range |

|---------|--------|------|-------------|---------|------|-------|---------|------|--------------------|-------|

| 0Eh     | AL/SW  | F1   | F0          | WP1     | WP0  | VBC   | FC      | TST  | Alarm & WP Control |       |

| 0Dh     | /Match | 0    | 0           | 10 mo   |      | Alarm | months  |      | Alarm Month        | 01-12 |

| 0Ch     | /Match | 0    | 10 (        | date    |      | Alarn | n date  |      | Alarm Date         | 01-31 |

| 0Bh     | /Match | 0    | Alarm 1     | 0 hours |      | Alarm | hours   |      | Alarm Hours        | 00-23 |

| 0Ah     | /Match | Ala  | arm 10 minu | ites    |      | Alarm | minutes |      | Alarm Minutes      | 00-59 |

| 09h     | /Match | Ala  | rm 10 seco  | nds     |      | Alarm | seconds |      | Alarm Seconds      | 00-59 |

| 08h     |        | 10 y | rears       |         |      | ye    | ars     |      | RTC Years          | 00-99 |

| 07h     | 0      | 0    | 0           | 10 mo   |      | mo    | nths    |      | RTC Month          | 1-12  |

| 06h     | 0      | 0    | 10          | date    |      | da    | ate     |      | RTC Date           | 1-31  |

| 05h     | 0      | 0    | 0           | 0       | 0    |       | day     |      | RTC Day            | 1-7   |

| 04h     | 0      | 0    | 10 h        | ours    |      | ho    | urs     |      | RTC Hours          | 0-23  |

| 03h     | 0      |      | 10 minutes  |         |      | min   | utes    |      | RTC Minutes        | 0-59  |

| 02h     | 0      |      | 10 seconds  | 5       |      | Sec   | onds    |      | RTC Seconds        | 0-59  |

| 01h     | /OSCEN | -    | CALS        | CAL4    | CAL3 | CAL2  | CAL1    | CAL0 | CAL/Control        |       |

| 00h     | LB     | AF   | CF          | POR     | AEN  | CAL   | W       | R    | RTC/Alarm Control  |       |

Note: When the device is first powered up, all registers should be treated as unknown and must be written. Otherwise, unpredictable behavior may result.

# **Register Description**

# Address Description

| 0Eh     | Alarm & W                                                                       | Alarm & WP Control                                              |                                 |                                                                                  |                                   |                                               |                           |                    |  |  |  |  |

|---------|---------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------|---------------------------|--------------------|--|--|--|--|

|         | D7                                                                              | D6                                                              | D5                              | D4                                                                               | D3                                | D2                                            | D1                        | D0                 |  |  |  |  |

|         | AL/SW                                                                           | F1                                                              | F0                              | WP1                                                                              | WP0                               | VBC                                           | FC                        | TST                |  |  |  |  |

| AL/SW   | the selected S<br>backed, read/                                                 | Square Wave F<br>write.                                         | req will be dri                 | ven on the AC                                                                    | S pin, and an a                   | pin as well as t<br>larm match on             | y sets the AF             | flag. Battery-     |  |  |  |  |

| F(1:0)  | both 0. Batter                                                                  | ry-backed.                                                      |                                 | t the frequenc                                                                   |                                   | oin when the C.                               | AL and AL/SV              | W bits are         |  |  |  |  |

|         |                                                                                 | 1 Hz 0                                                          | <u>1:0)</u><br>0 (default)<br>1 | 4(                                                                               | )96 Hz 1                          | ( <u>1:0)</u><br>0<br>1                       |                           |                    |  |  |  |  |

| WP1,WP0 | Write Protect                                                                   | . These bits co                                                 | ntrol the write                 | protection of                                                                    | the memory an                     | ray. Battery-ba                               | cked, read/wri            | te.                |  |  |  |  |

|         | No:<br>Bot<br>Bot                                                               | <u>ite-Protect add</u><br>ne<br>ttom 1/4<br>ttom 1/2<br>l array |                                 | P1         WP0           0         0           1         0           1         1 |                                   |                                               |                           |                    |  |  |  |  |

| VBC     |                                                                                 |                                                                 |                                 |                                                                                  |                                   | 80 µA (1mA in<br>current. Batter              |                           |                    |  |  |  |  |

| FC      | Fast Charge:                                                                    | Setting FC to                                                   | 1 (and VBC=1                    | ) causes appro                                                                   | ox. 1mA trickle<br>backed, read/w | e charge curren                               | t to be supplie           | d on $V_{BAK}$ .   |  |  |  |  |

| TST     | Invokes facto                                                                   | ory test mode. I                                                | Users should a                  | lways set this l                                                                 | oit to 0.                         |                                               |                           |                    |  |  |  |  |

| ADL     | Alarma M                                                                        | o 4 lo                                                          |                                 |                                                                                  |                                   |                                               |                           |                    |  |  |  |  |

| 0Dh     | Alarm – M<br>D7                                                                 | ontn<br>D6                                                      | D5                              | D4                                                                               | D3                                | D2                                            | D1                        | D0                 |  |  |  |  |

|         | M                                                                               | 0                                                               | 0                               | 10 Month                                                                         | Month.3                           | Month.2                                       | Month.1                   | Month.0            |  |  |  |  |

|         |                                                                                 | ÷                                                               | ÷                               |                                                                                  |                                   | select the Mont                               |                           | Woltu.0            |  |  |  |  |

| /M      | Match. Settin                                                                   | g this bit to a '                                               | 0' causes the l                 | Month value to                                                                   |                                   | alarm match le                                |                           | nis bit to a       |  |  |  |  |

| 0Ch     | Alarm – Da                                                                      |                                                                 |                                 |                                                                                  |                                   |                                               |                           |                    |  |  |  |  |

|         | D7                                                                              | D6                                                              | D5                              | D4                                                                               | D3                                | D2                                            | D1                        | D0                 |  |  |  |  |

|         | M                                                                               | 0                                                               | 10 date.1                       | 10 date.0                                                                        | Date.3                            | Date.2                                        | Date.1                    | Date.0             |  |  |  |  |

| /M      | Match: Settin                                                                   | ng this bit to a '                                              | 0' causes the l                 | Date value to b                                                                  |                                   | lect the Date va<br>larm match log<br>/write. |                           | s bit to a '1'     |  |  |  |  |

| 0Bh     | Alarm – Ho                                                                      |                                                                 | 0                               |                                                                                  | ,,                                |                                               |                           |                    |  |  |  |  |

|         | D7                                                                              | D6                                                              | D5                              | D4                                                                               | D3                                | D2                                            | D1                        | D0                 |  |  |  |  |

|         | M                                                                               | 0                                                               | 10 hours.1                      | 10 hours.0                                                                       | Hours.3                           | Hours2                                        | Hours.1                   | Hours.0            |  |  |  |  |

| /M      | Match: Settin                                                                   | g this bit to a '                                               | 0' causes the l                 | Hours value to                                                                   | be used in the                    | elect the Hours<br>alarm match lo             | value.<br>gic. Setting th | is bit to a '1'    |  |  |  |  |

|         | causes the match circuit to ignore the Hours value. Battery-backed, read/write. |                                                                 |                                 |                                                                                  |                                   |                                               |                           |                    |  |  |  |  |

| 0Ab     | Alarm M                                                                         | inutos                                                          |                                 |                                                                                  |                                   |                                               |                           |                    |  |  |  |  |

| 0Ah     | Alarm – M                                                                       |                                                                 | D5                              | D4                                                                               | D3                                | D2                                            | D1                        | D0                 |  |  |  |  |

| 0Ah     | D7                                                                              | D6                                                              | D5                              | D4                                                                               | D3                                | D2                                            | D1                        | D0                 |  |  |  |  |

| 0Ah     | <b>D7</b><br>M                                                                  | <b>D6</b><br>10 min.2                                           | 10 min.1                        | 10 min.0                                                                         | Min.3                             | D2<br>Min.2<br>eselect the Mir                | Min.1                     | <b>D0</b><br>Min.0 |  |  |  |  |

| 09h  | Alarm – Seconds                                                                                                                               |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----------------|------------------|-------------------|-------------------------------------|-----------------|--|--|--|--|

|      | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | M                                                                                                                                             | 10 sec.2                                                                                                                                                                                                                       | 10 sec.1                               | 10 sec.0        | Seconds.3        | Seconds.2         | Seconds.1                           | Seconds.0       |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | e for the second                       |                 |                  |                   |                                     | •               |  |  |  |  |

| M    |                                                                                                                                               |                                                                                                                                                                                                                                | o a '0' causes th<br>cuit to ignore th |                 |                  |                   | h logic. Setting                    | g this bit to a |  |  |  |  |

| 08h  | Timekeeping – Years                                                                                                                           |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

|      | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | 10 year.3                                                                                                                                     | 10 year.2                                                                                                                                                                                                                      | 10 year.1                              | 10 year.0       | Year.3           | Year.2            | Year.1                              | Year.0          |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | BCD digits of the                      |                 |                  |                   |                                     |                 |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | Each nibble of                         |                 |                  |                   |                                     |                 |  |  |  |  |

| )7h  | Timekeep                                                                                                                                      | oing – Mont                                                                                                                                                                                                                    | hs                                     |                 |                  |                   |                                     |                 |  |  |  |  |

|      | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | 0                                                                                                                                             | 0                                                                                                                                                                                                                              | 0                                      | 10 Month        | Month.3          | Month.2           | Month.1                             | Month.0         |  |  |  |  |

|      |                                                                                                                                               | Ŷ                                                                                                                                                                                                                              | for the month. I                       |                 |                  |                   |                                     |                 |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | the upper digit a                      |                 |                  |                   |                                     |                 |  |  |  |  |

|      | backed, rea                                                                                                                                   |                                                                                                                                                                                                                                |                                        |                 |                  |                   | -                                   |                 |  |  |  |  |

| )6h  | -                                                                                                                                             | <u> </u>                                                                                                                                                                                                                       | of the month                           |                 |                  |                   |                                     |                 |  |  |  |  |

|      | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | 0                                                                                                                                             | 0                                                                                                                                                                                                                              | 10 date.1                              | 10 date.0       | Date.3           | Date.2            | Date.1                              | Date.0          |  |  |  |  |

|      | Contains the BCD digits for the date of the month. Lower nibble contains the lower digit and operates from 0 to 9                             |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

|      |                                                                                                                                               | le contains the                                                                                                                                                                                                                | upper digit and                        | operates from   | 0 to 3. The rang | ge for the regist | er is 1-31. Bat                     | tery-backed,    |  |  |  |  |

|      | read/write.                                                                                                                                   |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

| )5h  |                                                                                                                                               | oing – Day o                                                                                                                                                                                                                   |                                        | _               |                  |                   |                                     |                 |  |  |  |  |

|      | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | 0                                                                                                                                             | 0                                                                                                                                                                                                                              | 0                                      | 0               | 0                | Day.2             | Day.1                               | Day.0           |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | value that correl                      |                 |                  |                   |                                     |                 |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | o 1. The user m                        | ust assign mear | ing to the day   | value, as the da  | y is not integra                    | ated with the   |  |  |  |  |

| 141. | date. Battery-backed, read/write.         Timekeeping – Hours                                                                                 |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

| )4h  | D7                                                                                                                                            | Ding – Hours<br>D6                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | D/                                                                                                                                            | Do                                                                                                                                                                                                                             |                                        | D4              | DS               |                   | DI                                  | D0              |  |  |  |  |

|      | 0                                                                                                                                             | 0                                                                                                                                                                                                                              | 10 hours.1                             | 10 hours.0      | Hours.3          | Hours2            | Hours.1                             | Hours.0         |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | of hours in 24-h                       |                 |                  |                   |                                     |                 |  |  |  |  |

|      | 9; upper nibble (two bits) contains the upper digit and operates from 0 to 2. The range for the register is 0-23. Battery-backed, read/write. |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

| )3h  |                                                                                                                                               | oing – Minu                                                                                                                                                                                                                    |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

| 511  | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

|      | 0<br>Contains th                                                                                                                              | 10 min.2                                                                                                                                                                                                                       | 10 min.1                               | 10 min.0        | Min.3            | Min.2             | $\frac{\text{Min.1}}{\text{Min.1}}$ | Min.0           |  |  |  |  |

|      |                                                                                                                                               | Contains the BCD value of minutes. Lower nibble contains the lower digit and operates from 0 to 9; upper nibble contains the upper minutes digit and operates from 0 to 5. The range for the register is 0-59. Battery-backed, |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

|      | read/write.                                                                                                                                   | e upper minut                                                                                                                                                                                                                  | es argit and oper                      |                 | 5. The funge for | t the register is | 0-59. Dattery-                      | ouckeu,         |  |  |  |  |

| )2h  |                                                                                                                                               | oing – Secon                                                                                                                                                                                                                   | ds                                     |                 |                  |                   |                                     |                 |  |  |  |  |

|      | D7                                                                                                                                            | D6                                                                                                                                                                                                                             | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

|      | 0                                                                                                                                             | 10 500 2                                                                                                                                                                                                                       | 10 522 1                               | 10 522 0        | Seconds 2        | Seconda 2         | Seconda 1                           | Sacanda         |  |  |  |  |

|      | -                                                                                                                                             | 10 sec.2                                                                                                                                                                                                                       | 10 sec.1<br>of seconds. Low            | 10 sec.0        | Seconds.3        | Seconds.2         | Seconds.1                           | Seconds.0       |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | and operates from                      |                 |                  |                   |                                     |                 |  |  |  |  |

|      | Contains th                                                                                                                                   | - apper digit t                                                                                                                                                                                                                | operates not                           |                 |                  |                   |                                     |                 |  |  |  |  |

| )1h  | CAL/C                                                                                                                                         | ontrol                                                                                                                                                                                                                         |                                        |                 |                  |                   |                                     |                 |  |  |  |  |

|      |                                                                                                                                               |                                                                                                                                                                                                                                | D5                                     | D4              | D3               | D2                | D1                                  | D0              |  |  |  |  |

| VIN    | CAL/Control                                                                                                                                                                                                   |    |      |       |       |       |       |       |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|-------|-------|-------|-------|-------|

|        | D7                                                                                                                                                                                                            | D6 | D5   | D4    | D3    | D2    | D1    | D0    |

|        | OSCEN                                                                                                                                                                                                         | -  | CALS | CAL.4 | CAL.3 | CAL.2 | CAL.1 | CAL.0 |

| /OSCEN | Oscillator Enable. When set to 1, the oscillator is halted. When set to 0, the oscillator runs. Disabling the                                                                                                 |    |      |       |       |       |       |       |

|        | oscillator can save battery power during storage. On an initial power-up of $V_{DD}$ with or without $V_{BAK}$ , this bit is internally set to 1, which turns off the oscillator. Battery-backed, read/write. |    |      |       |       |       |       |       |

| CALS    | Calibration Sign: Determines if the calibration adjustment is applied as an addition to or as a subtraction from |

|---------|------------------------------------------------------------------------------------------------------------------|

|         | the time-base. This bit can be written only when CAL=1. Battery-backed, read/write.                              |

| CAL.4-0 | Calibration Code: These five bits control the calibration of the clock. These bits can be written only when      |

|         | CAL=1. Battery-backed, read/write.                                                                               |

| 00h | RTC/Alarn                                                                                                                                                                                                                                                                                                                                                                                                                                | n Control                                                                                                                                                                                                             |                |                                                         |                |                |                |              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------|----------------|----------------|----------------|--------------|

|     | D7                                                                                                                                                                                                                                                                                                                                                                                                                                       | D6                                                                                                                                                                                                                    | D5             | D4                                                      | D3             | D2             | D1             | D0           |

|     | LB                                                                                                                                                                                                                                                                                                                                                                                                                                       | AF                                                                                                                                                                                                                    | CF             | POR                                                     | AEN            | CAL            | W              | R            |

| LB  | Low Battery Flag: If the $V_{BAK}$ source drops to a voltage level insufficient to operate the RTC/alarm, this bit will be set to '1'. All registers need to be re-initialized since the battery-backed register values should be treated as unknown. The user should clear it to '0' when initializing the system. Battery-backed. Read/Write (internally set, user can clear bit by writing to a '0').                                 |                                                                                                                                                                                                                       |                |                                                         |                |                |                |              |

| AF  |                                                                                                                                                                                                                                                                                                                                                                                                                                          | Alarm Flag: This read-only bit is set to 1 when the time/date match the values stored in the alarm registers with the Match $bit(s) = 0$ . It is cleared when the RTC/Alarm Control register is read. Battery-backed. |                |                                                         |                |                |                |              |

| CF  | Century Overflow Flag: This read-only bit is set to a 1 when the values in the years register overflows from 99 to 00. This indicates a new century, such as going from 1999 to 2000 or 2099 to 2100. The user should record the new century information as needed. This bit is cleared when the RTC/Alarm Control register is read. Battery-backed.                                                                                     |                                                                                                                                                                                                                       |                |                                                         |                |                |                |              |

| POR | Power On Re                                                                                                                                                                                                                                                                                                                                                                                                                              | set Flag: When                                                                                                                                                                                                        |                | low V <sub>SW</sub> , the Point by writing to           |                | set to '1'. Ba | attery-backed. |              |

| AEN | Read/Write (internally set, user can clear bit by writing to a '0').         Alarm Enable: This bit enables the alarm function. When AEN is set (and CAL cleared), the ACS pin operates as an active-low alarm and the AF flag function is enabled. The function of the ACS pin is detailed in Table 3. When AEN is cleared, no new alarm events will occur but the AF flag and ACS pin will not be cleared. Battery-backed, read/write. |                                                                                                                                                                                                                       |                |                                                         |                |                |                |              |

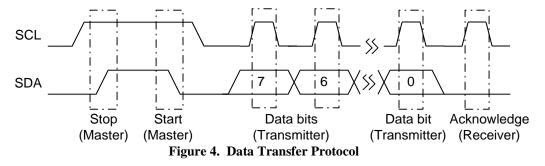

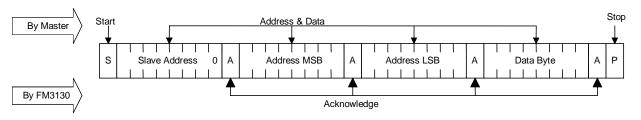

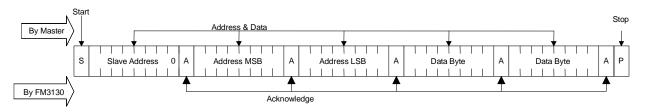

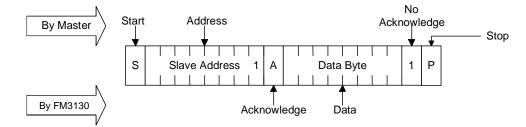

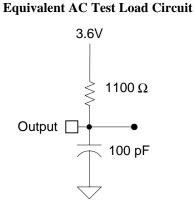

| CAL | Calibration Mode: When CAL is set to '1', the clock enters calibration mode. When CAL is set to '0', the clock operates normally, and the ACS pin is controlled by the RTC alarm. Battery-backed, read/write.                                                                                                                                                                                                                            |                                                                                                                                                                                                                       |                |                                                         |                |                |                |              |